贴片共模电感引脚定义 共模电感成品展示共模电感在日常生活中常见的就是计算机应用中,计算机内部的主板上混合了各种高频电路、数字电路和模拟电路,它们工作时会产生大量高频电磁波互相干扰,这就是EMI。EMI还会通过主板布线或外接线缆向外发射,造成电磁辐射污染,不但影响其他的电子设备正常工作,还对人体有害。

贴片共模电感引脚定义

对的主板布线设计而言,时钟走线大多会采用屏蔽措施或者靠近地线以降低EMI。对多层PCB设计,在相邻的PCB走线层会采用开环原则,导线从一层到另一层,在设计上就会避免导线形成环状。如果走线构成闭环,就起到了天线的作用,会增强EMI辐射强度。信号线的不等长同样会造成两条线路阻抗不平衡而形成共模干扰,因此,在板卡设计中都会将信号线以蛇形线方式处理使其阻抗尽可能的一致,减弱共模干扰。同时,蛇形线在布线时也会限度地减小弯曲的摆幅,以减小环形区域的面积,从而降低辐射强度。

共模电感缺失=防EMI性能低下?这样的说法显然是颇为片面的。诚然,由于国家的EMI相关规范并不健全,部分厂商为了省料就钻了这个空子,在整体防EMI性能上都大肆省料压缩成本(其中就包括共模电感的省略),这样做的直接后果就是主板防EMI性能极其低下;但是对于那些整体设计,用料不缩水的主板,即使没有共模电感,其整体防EMI性能仍能达到相关要求,这样的产品仍然是合格的。因此,单纯就是否有共模电感这一点来判断主板的优劣并不恰当.

贴片共模电感引脚定义,由于可以通过控制B总,使之小于B饱和,从而防止芯体发生磁饱和现象,有以下法则:式中,是差模峰值电流,Bmax是磁通量的偏离,n是线圈的匝数,A是环形线圈的横截面积。Ldm是线圈的差模电感。共模扼流圈的差模电感可以按如下方法测得:将其一引腿两端短接,然后测量另外两腿间的电感,其示值即为共模扼流圈的差模电感。

在环形共模电感的特殊场合中,每条引线中的差模电流密度可假定是相等的,且方向相反。所以由此而产生的磁场必定在环形磁芯周边上的总和为0,而在其外部则不为0!磁芯的作用就好像它在线圈绕组的间隙处裂为两半时所表现出来的效果一样。每个绕组在环形线圈一半的区域内产生磁场,意指穿过空气的磁场必定会形成自封闭回路。

共模扼流圈能发挥一定的作用是由于μcm比μdm大好几个数量级的缘故,因为共模电流通常很小,可以通过使L/D保持在较低值来获得更小的μdm。为了得到共模电感,同时又要使差模电感小,是采用横截面积较大的磁芯绕制成多匝线圈。采用较大的螺旋管磁芯,也并非一定要这样的磁芯,可在共模扼流圈内并入有效的差模电感。因为差模磁通是远离磁芯(环形结构)的,因此可能会产生极强的辐射。尤其是滤波器安装在PCB板上的情况下,这种辐射可以耦合到电源线,使传导发射增强。当磁性材料被带到场内时(例如,环形磁芯放置在铁壳里),差模磁导率就可能会显著地增加,从而由于差模电流而导致磁芯的饱和。

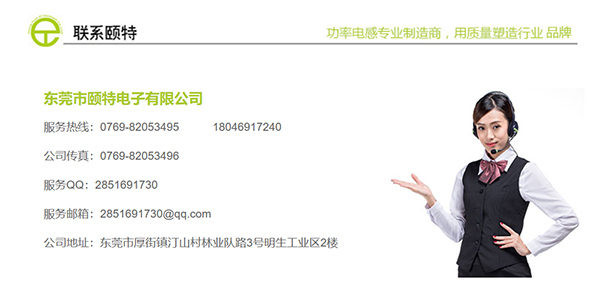

想要了解更多贴片共模电感引脚定义,欢迎咨询!

-THE END -

版权东莞颐特电子所有 如涉及版权问题请及时联系处理

电感丨贴片电感丨一体成型电感丨共模电感丨绕线电感丨磁环电感丨功率电感丨电感厂家丨颐特电子